# GR740 Quad Core LEON4 SPARC V8 Processor

#### Features

- Fault-tolerant quad-processor SPARC V8 integer unit with 7-stage pipeline, 8 register windows, 4x4 KiB instruction and 4x4 KiB data caches.

- Double-precision IEEE-754 floating point units

- 2 MiB Level-2 cache

- 64-bit PC100 SDRAM memory interface with Reed-Solomon EDAC\*

- 8/16-bit PROM/IO interface with EDAC\*

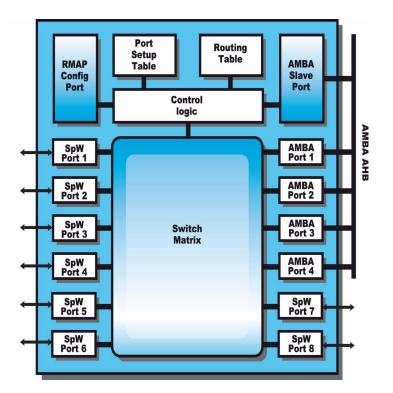

- SpaceWire router with eight SpaceWire links

- 2x 10/100/1000 Mbit Ethernet interfaces\*

- PCI Initiator/Target interface\*

- MIL-STD-1553B interface\*

- 2x CAN 2.0 controller interface\*

- 2x UART, SPI, Timers and watchdog, 16+22 GPIO\*

- CPU and I/O memory management units

- SpaceWire Time Distribution Protocol controller and support for time synchronisation

- JTAG, Ethernet\* and SpaceWire\* debug links \* Interfaces have shared pins

#### Description

The GR740 device is a radiation-hard system-onchip featuring a quad-core fault-tolerant LEON4 SPARC V8 processor, eight port SpaceWire router, PCI initiator/target interface, MIL-STD-1553B interface, CAN 2.0 interfaces and 10/100/1000 Mbit Ethernet interfaces.

## Specification

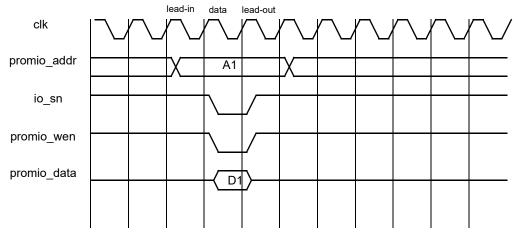

- System frequency: 250 MHz

- Main memory interface: PC100 SDRAM

- SpaceWire router with SpaceWire links: 300

Mbit/s

- 33 MHz PCI 2.3 initiator/target interface

- Ethernet 10/100/1000 Mbit MACs

- CCGA625 / CLGA625 / PBGA625 package

## Applications

The GR740 device is targeted at high-performance general purpose processing. The architecture is suitable for both symmetric and asymmetric multiprocessing. Shared resources can be monitored to support mixed-criticality applications. SPĄRC

#### **Table of contents**

| 1 | Intro | Introduction                                                  |    |  |  |

|---|-------|---------------------------------------------------------------|----|--|--|

|   | 1.1   | Scope                                                         |    |  |  |

|   | 1.2   | Data sheet status                                             |    |  |  |

|   | 1.3   | Updates and feedback                                          |    |  |  |

|   | 1.4   | Software support                                              |    |  |  |

|   | 1.5   | Development board                                             |    |  |  |

|   | 1.6   | Performance, power consumption and radiation tolerance        |    |  |  |

|   | 1.7   | Reference documents                                           |    |  |  |

|   | 1.8   | Document revision history                                     |    |  |  |

|   | 1.9   | Acronyms                                                      |    |  |  |

|   | 1.10  | Definitions                                                   |    |  |  |

|   | 1.11  | Register descriptions                                         |    |  |  |

| 2 | Arch  | itecture                                                      |    |  |  |

|   | 2.1   | Overview                                                      |    |  |  |

|   | 2.2   | Cores                                                         |    |  |  |

|   | 2.3   | Memory map                                                    |    |  |  |

|   | 2.4   | Interrupts                                                    |    |  |  |

|   | 2.5   | Plug & play and bus index information                         |    |  |  |

| 3 | Signa | als                                                           | 30 |  |  |

| 2 | 3.1   | Bootstrap signals                                             |    |  |  |

|   | 3.2   | Configuration for flight                                      |    |  |  |

|   | 3.3   | Pin multiplexing                                              |    |  |  |

|   | 3.4   | Complete signal list                                          |    |  |  |

|   | 3.5   | Pin driver configuration                                      |    |  |  |

|   | 3.6   | Initial signal state                                          |    |  |  |

| 4 | Cloc  | king and reset                                                |    |  |  |

|   | 4.1   | Clock inputs                                                  |    |  |  |

|   | 4.2   | Clock loop for SDRAM                                          |    |  |  |

|   | 4.3   | Reset scheme                                                  |    |  |  |

|   | 4.4   | Clock multiplexing for main system clock, SDRAM and SpaceWire |    |  |  |

|   | 4.5   | PLL control and configuration                                 |    |  |  |

|   | 4.6   | PLL watchdog                                                  |    |  |  |

|   | 4.7   | PCI clock                                                     |    |  |  |

|   | 4.8   | MIL-STD-1553B clock                                           |    |  |  |

|   | 4.9   | Clock gating unit                                             |    |  |  |

|   | 4.10  | Debug AHB bus clocking                                        |    |  |  |

| 5 | Tech  | Technical notes                                               |    |  |  |

| 0 | 5.1   | GRLIB AMBA plug&play scanning                                 |    |  |  |

|   | 5.2   | Processor register file initialisation and data scrubbing     |    |  |  |

|   | 5.3   | PROM-less systems and SpaceWire RMAP                          |    |  |  |

|   | 5.4   | System integrity and debug communication links                |    |  |  |

|   | 5.5   | Separation and ASMP configurations                            |    |  |  |

|   | 5.6   | Clock gating                                                  |    |  |  |

|   | 5.7   | Software portability                                          |    |  |  |

|   | 5.8   | Level-2 cache                                                 |    |  |  |

|   | 5.9   | Time synchronisation                                          |    |  |  |

|   | 5.10  | Bridges, posted-writes and ERROR response propagation         |    |  |  |

|   | -     |                                                               |    |  |  |

## GR740

| 6  | LEO   | N4 - Fault-tolerant High-performance SPARC V8 32-bit Processor |    |

|----|-------|----------------------------------------------------------------|----|

|    | 6.1   | Overview                                                       |    |

|    | 6.2   | LEON4 integer unit                                             |    |

|    | 6.3   | Cache system                                                   | 61 |

|    | 6.4   | Memory management unit                                         | 64 |

|    | 6.5   | Floating-point unit                                            |    |

|    | 6.6   | Co-processor interface                                         |    |

|    | 6.7   | AMBA interface                                                 |    |

|    | 6.8   | Multi-processor system support                                 |    |

|    | 6.9   | ASI assignments                                                |    |

|    | 6.10  | Configuration registers                                        |    |

|    | 6.11  | Software considerations                                        |    |

| 7  | Float | ing-point Control Unit                                         |    |

|    | 7.1   | Floating-Point register file                                   |    |

|    | 7.2   | Floating-Point State Register (FSR)                            |    |

|    | 7.3   | Floating-Point Exceptions and Floating-Point Deferred-Queue    |    |

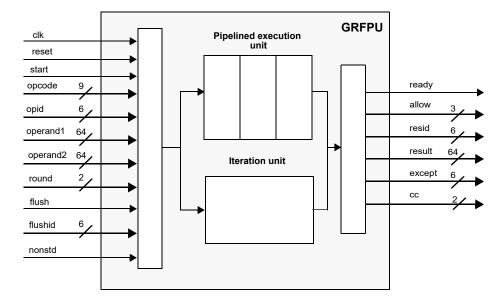

| 8  | High  | -performance IEEE-754 Floating-point Unit                      |    |

|    | 8.1   | Overview                                                       |    |

|    | 8.2   | Functional description                                         |    |

| 9  | Leve  | 1 2 Cache controller                                           |    |

|    | 9.1   | Overview                                                       |    |

|    | 9.2   | Configuration                                                  |    |

|    | 9.3   | Operation                                                      |    |

|    | 9.4   | Registers                                                      |    |

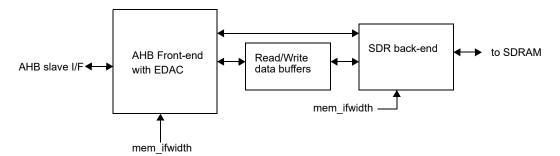

| 10 | SDR   | AM Memory Controller with Reed-Solomon EDAC                    |    |

|    | 10.1  | Overview                                                       |    |

|    | 10.2  | Operation                                                      |    |

|    | 10.3  | Limitations                                                    |    |

|    | 10.4  | SDRAM back-end operation                                       |    |

|    | 10.5  | Fault-tolerant operation                                       |    |

|    | 10.6  | Registers                                                      |    |

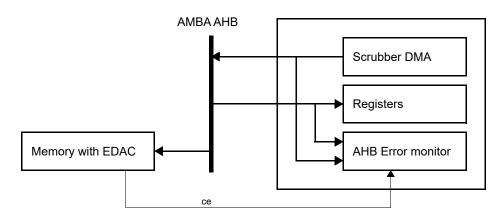

| 11 | Mem   | ory Scrubber and AHB Status Register                           |    |

|    | 11.1  | Overview                                                       |    |

|    | 11.2  | Operation                                                      |    |

|    | 11.3  | Registers                                                      |    |

| 12 | IOM   | MU - Bridge connecting Master I/O AHB bus                      |    |

|    | 12.1  | Overview                                                       |    |

|    | 12.2  | Bridge operation                                               |    |

|    | 12.3  | General access protection and address translation              |    |

|    | 12.4  | Access Protection Vector                                       |    |

|    | 12.5  | IO Memory Management Unit (IOMMU) functionality                |    |

|    | 12.6  | Fault-tolerance                                                |    |

|    | 12.7  | Statistics                                                     |    |

|    | 12.8  | ASMP support                                                   |    |

|    | 12.9  | Registers                                                      |    |

| 13 | Space | eWire router                                                   |    |

|    | 13.1  | Overview                                                       |    |

|    |       |                                                                |    |

#

|    | 13.2  | Operation                                           |  |

|----|-------|-----------------------------------------------------|--|

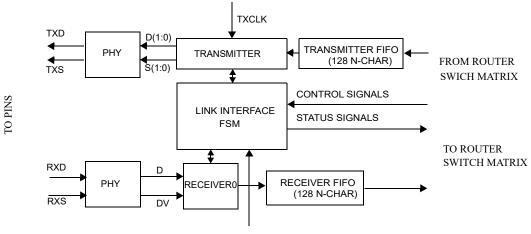

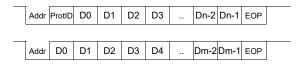

|    | 13.3  | SpaceWire ports                                     |  |

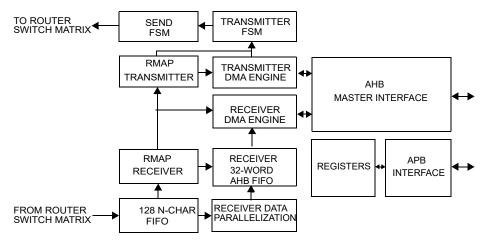

|    | 13.4  | AMBA ports                                          |  |

|    | 13.5  | Configuration port                                  |  |

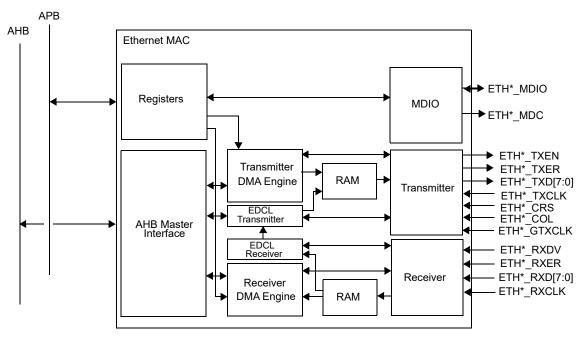

| 14 | Gigał | bit Ethernet Media Access Controller (MAC)          |  |

|    | 14.1  | Overview                                            |  |

|    | 14.2  | Operation                                           |  |

|    | 14.3  | Tx DMA interface                                    |  |

|    | 14.4  | Rx DMA interface                                    |  |

|    | 14.5  | MDIO Interface                                      |  |

|    | 14.6  | Ethernet Debug Communication Link (EDCL)            |  |

|    | 14.7  | Media Independent Interfaces                        |  |

|    | 14.8  | Registers                                           |  |

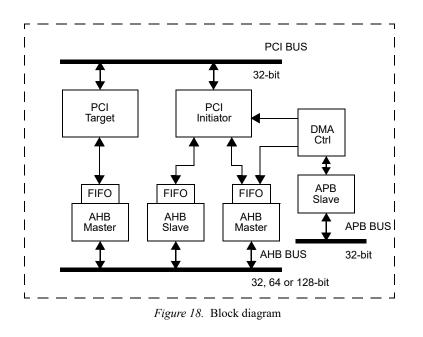

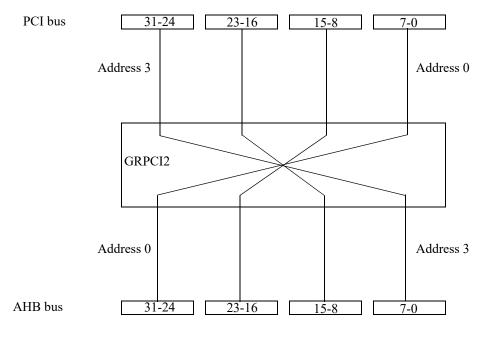

| 15 | 32-bi | t PCI/AHB bridge                                    |  |

|    | 15.1  | Overview                                            |  |

|    | 15.2  | Configuration                                       |  |

|    | 15.3  | Operation                                           |  |

|    | 15.4  | PCI Initiator interface                             |  |

|    | 15.5  | PCI Target interface                                |  |

|    | 15.6  | DMA Controller                                      |  |

|    | 15.7  | PCI trace buffer                                    |  |

|    | 15.8  | Interrupts                                          |  |

|    | 15.9  | Reset                                               |  |

|    | 15.10 | Registers                                           |  |

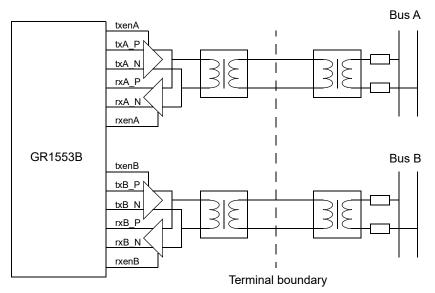

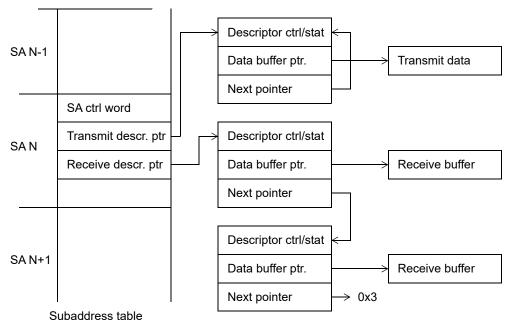

| 16 | MIL-  | STD-1553B / AS15531 Interface                       |  |

|    | 16.1  | Overview                                            |  |

|    | 16.2  | Electrical interface                                |  |

|    | 16.3  | Operation                                           |  |

|    | 16.4  | Bus Controller Operation                            |  |

|    | 16.5  | Remote Terminal Operation                           |  |

|    | 16.6  | Bus Monitor Operation                               |  |

|    | 16.7  | Clocking and reset                                  |  |

|    | 16.8  | Registers                                           |  |

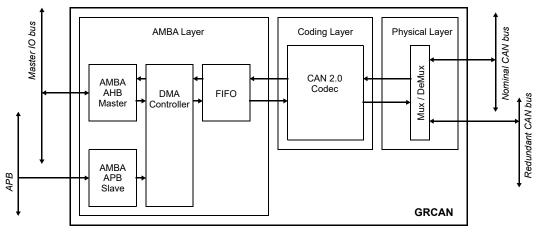

| 17 | CAN   | 2.0 Controllers with DMA                            |  |

|    | 17.1  | Overview                                            |  |

|    | 17.2  | Interface                                           |  |

|    | 17.3  | Protocol                                            |  |

|    | 17.4  | Status and monitoring                               |  |

|    | 17.5  | Transmission                                        |  |

|    | 17.6  | Reception                                           |  |

|    | 17.7  | Global reset and enable                             |  |

|    | 17.8  | Interrupt                                           |  |

|    | 17.9  | Registers                                           |  |

|    | 17.10 | Memory mapping                                      |  |

| 18 | Bridg | e connecting Slave I/O AHB bus to Processor AHB bus |  |

|    | 18.1  | Overview                                            |  |

|    | 18.2  | Operation                                           |  |

|    | 18.3  | Registers                                           |  |

|    |       |                                                     |  |

## GR740

|--|

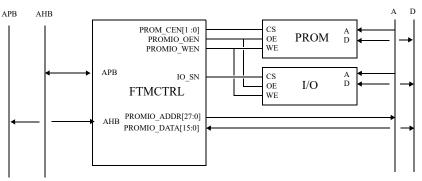

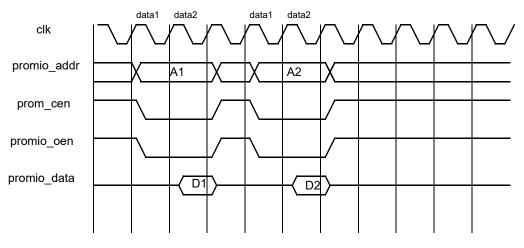

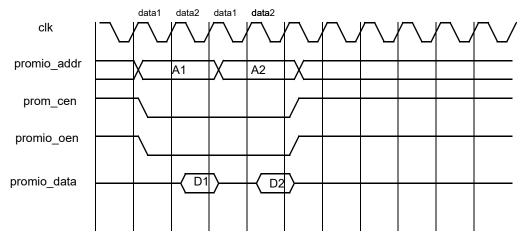

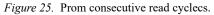

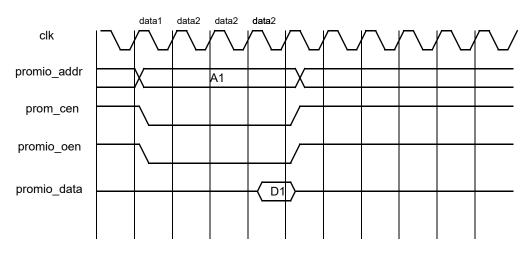

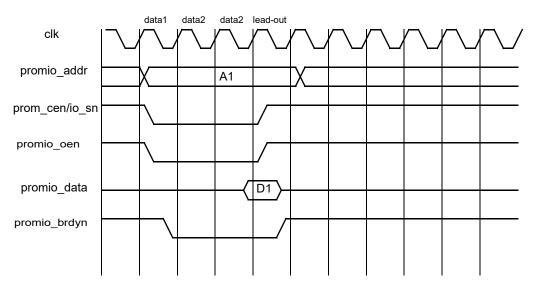

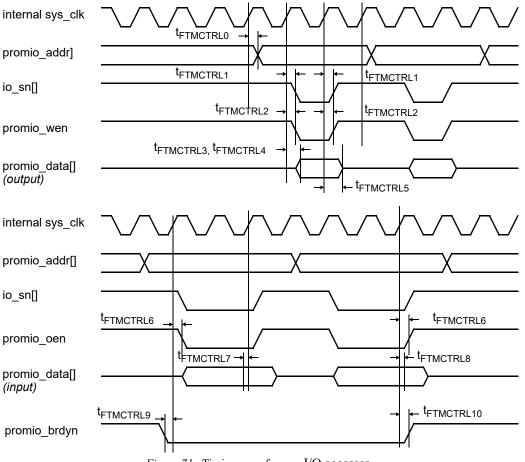

| 19 | Fault-tolerant 8/16-bit PROM/IO Memory Interface               |     |

|----|----------------------------------------------------------------|-----|

|    | 19.1 Overview                                                  |     |

|    | 19.2 PROM access                                               |     |

|    | 19.3 Memory mapped IO                                          |     |

|    | 19.4 8-bit and 16-bit PROM access                              |     |

|    | 19.5 8- and 16-bit I/O access                                  |     |

|    | 19.6 Burst cycles                                              |     |

|    | 19.7 Memory EDAC                                               |     |

|    | 19.8 Bus Ready signalling                                      |     |

|    | 19.9 Registers                                                 |     |

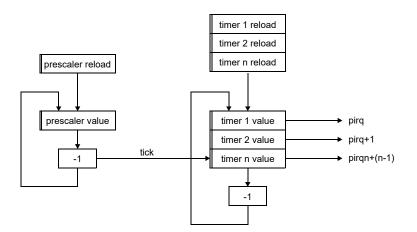

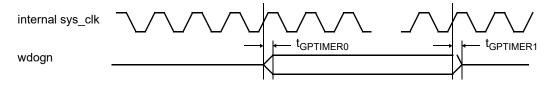

| 20 | General Purpose Timer Units                                    |     |

|    | 20.1 Overview                                                  |     |

|    | 20.2 Operation                                                 |     |

|    | 20.3 Registers                                                 |     |

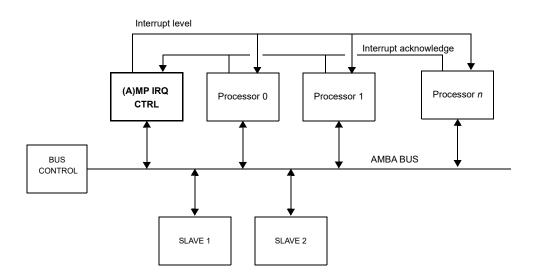

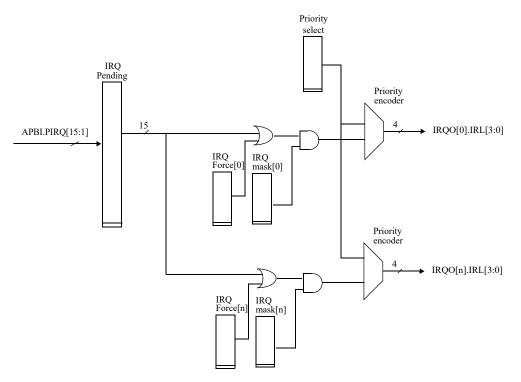

| 21 | Multiprocessor Interrupt Controller with extended ASMP support | 309 |

| 21 | 21.1 Overview                                                  |     |

|    | 21.2 Operation                                                 |     |

|    | 21.2 Operation<br>21.3 Registers                               |     |

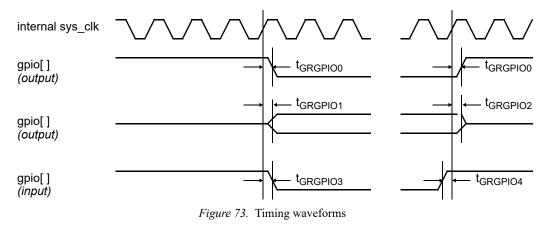

| 22 | General Purpose I/O Ports                                      |     |

|    | 22.1 Overview                                                  |     |

|    | 22.1 Overview                                                  |     |

|    | 22.3 Registers                                                 |     |

|    | 5                                                              |     |

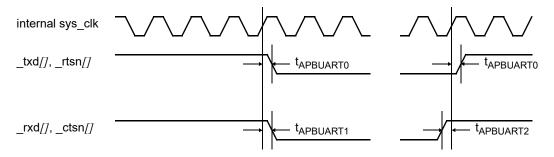

| 23 | UART Serial Interfaces                                         |     |

|    | 23.1 Overview                                                  |     |

|    | 23.2 Operation                                                 |     |

|    | 23.3 Baud-rate generation                                      |     |

|    | 23.4 Loop back mode                                            |     |

|    | 23.5 FIFO debug mode                                           |     |

|    | 23.6 Interrupt generation                                      |     |

|    | 23.7 Registers                                                 |     |

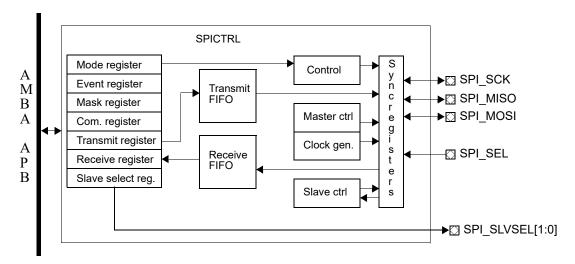

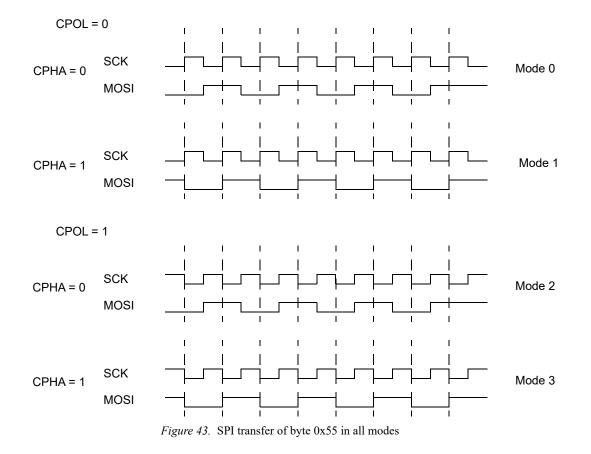

| 24 | SPI Controller supporting master and slave operation           |     |

|    | 24.1 Overview                                                  |     |

|    | 24.2 Operation                                                 |     |

|    | 24.3 Registers                                                 |     |

| 25 | Clock gating unit                                              |     |

|    | 25.1 Overview                                                  |     |

|    | 25.2 Operation                                                 |     |

|    | 25.3 Registers                                                 |     |

| 26 | LEON4 Statistics Unit (Performance Counters)                   |     |

| 20 | 26.1 Overview                                                  |     |

|    | 26.2 Multiple APB interfaces                                   |     |

|    | 26.3     Registers                                             |     |

| 27 |                                                                |     |

| 27 | AHB Status Registers                                           |     |

|    | 27.1 Overview                                                  |     |

|    | 27.2 Operation                                                 |     |

|    | 27.3 Registers                                                 |     |

#

| 28 | Register for bootstrap signals                             |  |

|----|------------------------------------------------------------|--|

|    | 28.1 Overview                                              |  |

|    | 28.2 Operation                                             |  |

|    | 28.3 Registers                                             |  |

| 29 | Temperature sensor controller                              |  |

|    | 29.1 Overview                                              |  |

|    | 29.2 Operation                                             |  |

|    | 29.3 Registers                                             |  |

| 30 | Register Bank For I/O and PLL configuration registers      |  |

|    | 30.1 Overview                                              |  |

|    | 30.2 Operation                                             |  |

|    | 30.3 Registers                                             |  |

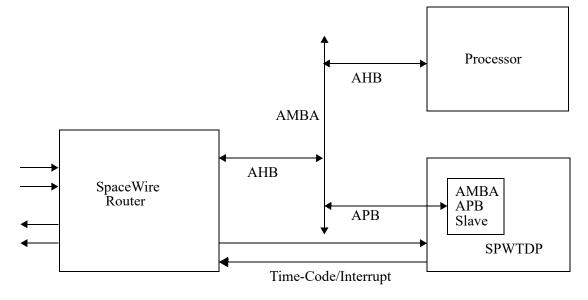

| 31 | SpaceWire - Time Distribution Protocol Controller          |  |

| -  | 31.1 Overview                                              |  |

|    | 31.2 Protocol                                              |  |

|    | 31.3 Functionality                                         |  |

|    | 31.4 Registers                                             |  |

| 32 | Bridge connecting Debug AHB bus to Processor AHB bus       |  |

| -  | 32.1 Overview                                              |  |

|    | 32.2 Operation                                             |  |

|    | 32.3 Registers                                             |  |

| 33 | LEON4 Hardware Debug Support Unit                          |  |

|    | 33.1 Overview                                              |  |

|    | 33.2 Operation                                             |  |

|    | 33.3 AHB Trace Buffer                                      |  |

|    | 33.4 Instruction trace buffer                              |  |

|    | 33.5 DSU memory map                                        |  |

|    | 33.6 DSU registers                                         |  |

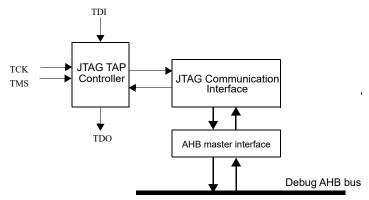

| 34 | JTAG Debug Link with AHB Master Interface                  |  |

|    | 34.1 Overview                                              |  |

|    | 34.2 Operation                                             |  |

|    | 34.3 Registers                                             |  |

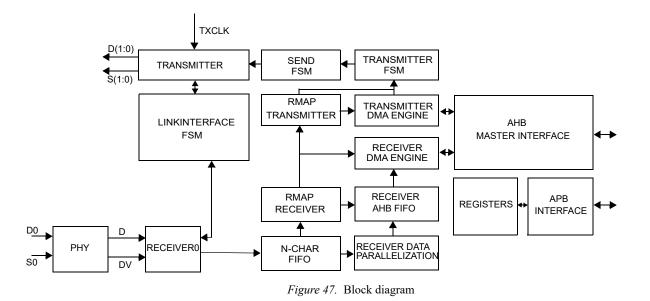

| 35 | SpaceWire Debug Link                                       |  |

|    | 35.1 Overview                                              |  |

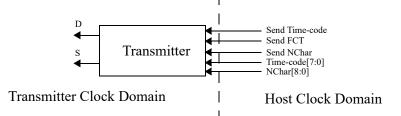

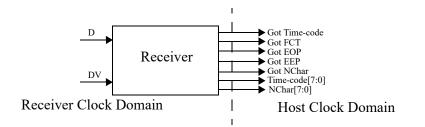

|    | 35.2 Operation                                             |  |

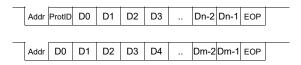

|    | 35.3 Link interface                                        |  |

|    | 35.4 Time-Code distribution                                |  |

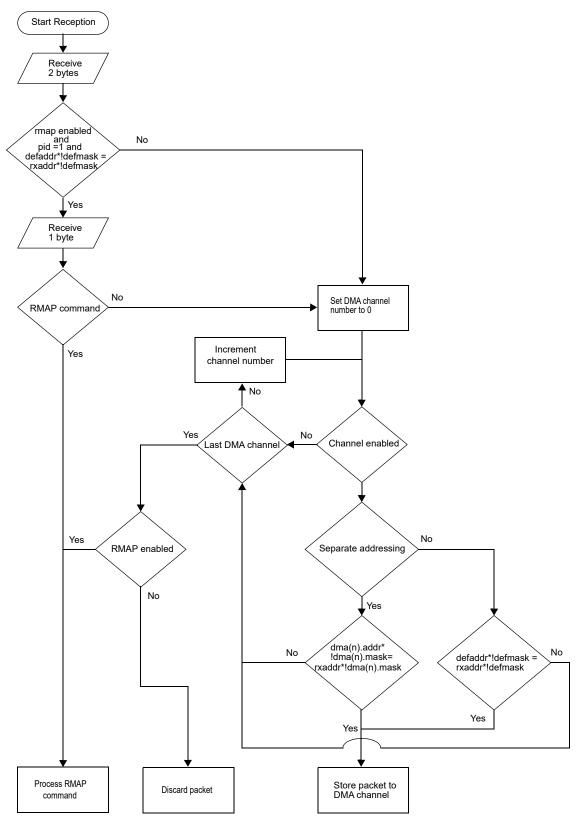

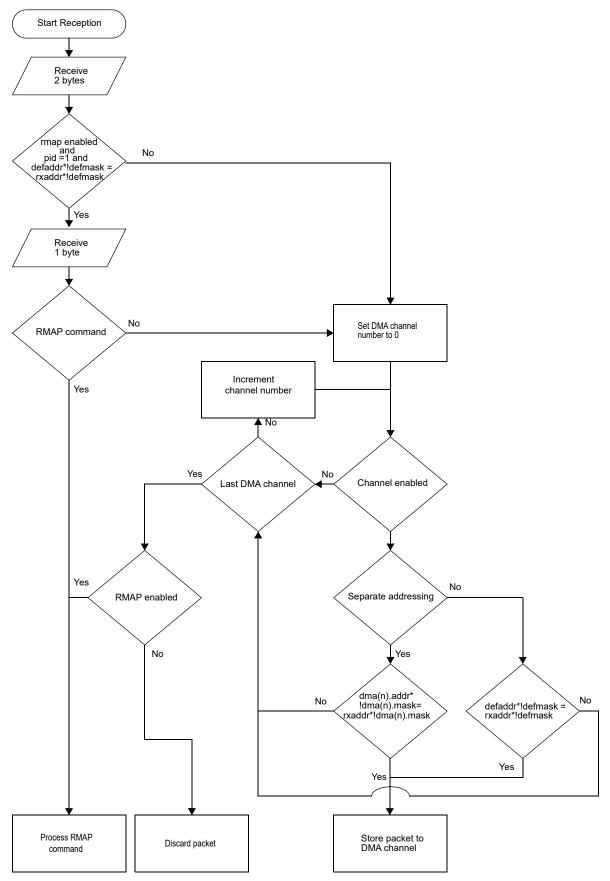

|    | 35.5 Receiver DMA channels                                 |  |

|    | 35.6 Transmitter DMA channels                              |  |

|    | <ul> <li>35.7 RMAP</li> <li>35.8 AMBA interface</li> </ul> |  |

|    |                                                            |  |

| 26 | 35.9 Registers                                             |  |

| 36 | AHB Trace buffer tracing Master I/O AHB bus                |  |

|    | 36.1 Overview                                              |  |

|    | <ul> <li>36.2 Operation</li></ul>                          |  |

|    | JU.J REGISICIS                                             |  |

#

## GR740

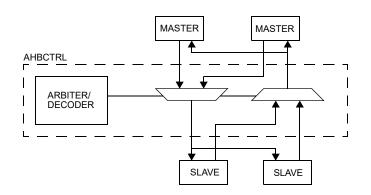

| 37 | AMBA    | AAHB controller with plug&play support     |  |

|----|---------|--------------------------------------------|--|

|    | 37.1    | Overview                                   |  |

|    | 37.2    | Operation                                  |  |

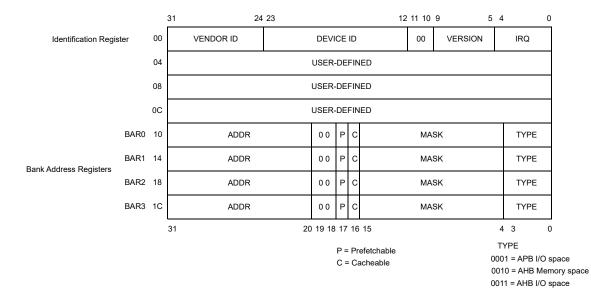

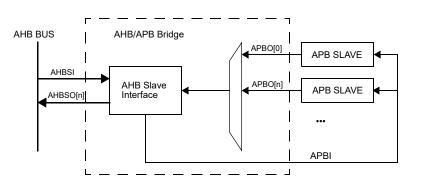

| 38 | AMBA    | AAHB/APB bridge with plug&play support     |  |

|    | 38.1    | Overview                                   |  |

|    | 38.2    | Operation                                  |  |

| 39 | Electri | cal description                            |  |

|    | 39.1    | Absolute maximum ratings                   |  |

|    | 39.2    | Recommended operating conditions           |  |

|    | 39.3    | Input and output signal DC characteristics |  |

|    | 39.4    | Power supplies                             |  |

|    | 39.5    | AC characteristics                         |  |

| 40 | Mecha   | nical description                          |  |

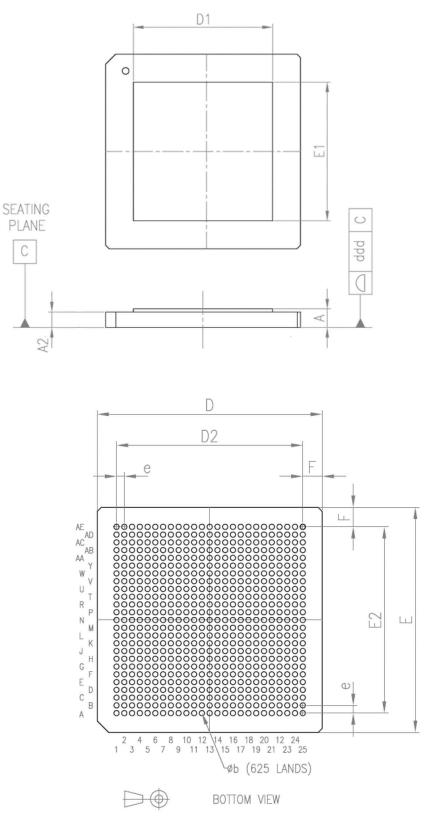

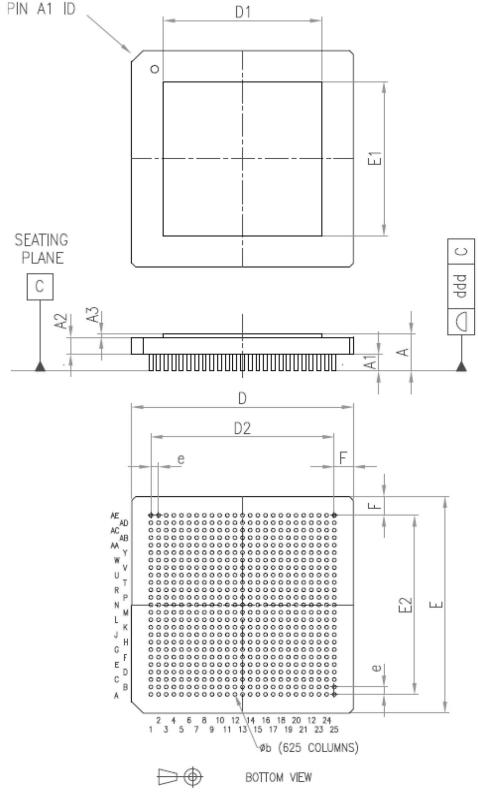

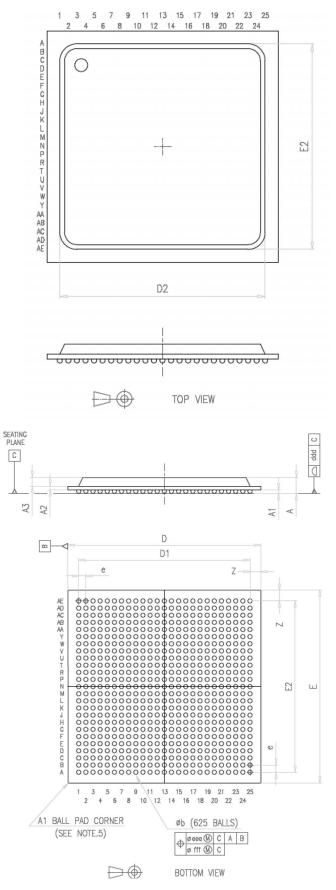

|    | 40.1    | Component and package                      |  |

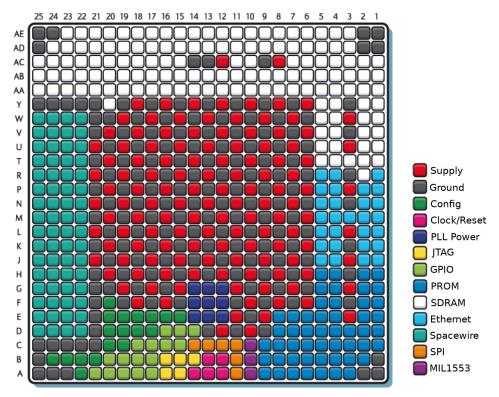

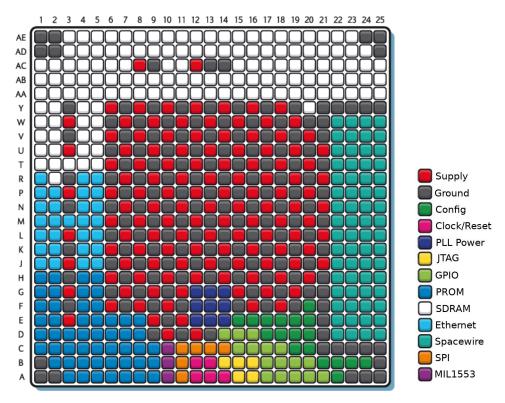

|    | 40.2    | Package placement diagram                  |  |

|    | 40.3    | Pin assignment                             |  |

|    | 40.4    | Package drawing                            |  |

| 41 | Tempe   | erature and thermal resistance             |  |

| 42 | Orderi  | ng information                             |  |

| 43 | Errata  |                                            |  |

|    | 43.1    | Overview                                   |  |

|    | 43.2    | Errata descriptions                        |  |

|    |         |                                            |  |

## 1 Introduction

## 1.1 Scope

This document is the user manual and data sheet for the GR740 device. The GR740 was developed in an activity funded by the European Space Agency.

This version of the document describes silicon revision 1 of the GR740 device. Users of earlier prototype silicon should refer to the latest 1.x version of the data sheet, available from www.gaisler.com/ GR740.

### **1.2** Data sheet status

This document is a combined data sheet and user manual. The data sheet information is contained in sections 39-42. The different maturity stages of the document are:

- Advanced data sheet Product in development

- Preliminary data sheet Shipping prototype

- Data sheet Shipping space-grade product

## **1.3 Updates and feedback**

Updates are available at http://www.gaisler.com/gr740

Feedback: support@gaisler.com

For commercial questions please contact sales@gaisler.com

## 1.4 Software support

The GR740 design is supported by standard toolchains provided by Frontgrade Gaisler. Toolchains can be downloaded from http://www.gaisler.com.

#### **1.5** Development board

Development boards with the GR740 device is available. Please see www.gaisler.com/GR740.

#### 1.6 Performance, power consumption and radiation tolerance

Technical notes on GR740 validation and benchmarking are available at www.gaisler.com/GR740.

### **1.7** Reference documents

| [AMBA]              | AMBA Specification, Rev 2.0, ARM Limited                                                                                                          |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| [CCSDS]             | Time Code Formats, CCSDS 301.0-B-4, Blue Book, Issue 4, November 2010, http://www.CCSDS.org                                                       |

| [FTMBCH]            | FTMCTRL: BCH EDAC with multiple 8-bit wide PROM and SRAM banks, GRLIB-AN-0003, http://www.gaisler.com/notes                                       |

| [RMAP]              | Space engineering: SpaceWire - Remote memory access protocol, ECSS-E-ST-50-52C, February 2010                                                     |

| [GR-AN-0004]        | Handling of External Memory EDAC Errors in LEON/GRLIB Systems, GRLIB-AN-0004, http://www.gaisler.com/notes                                        |

| [SPARC]             | The SPARC Architecture Manual, Version 8, SPARC International Inc.                                                                                |

| [SPW]               | Space engineering: SpaceWire - Links, nodes, routers and networks, ECSS-E-ST-50-12C, July 2008                                                    |

| [SPWBT]             | Booting a LEON system over SpaceWire RMAP, GRLIB-AN-0002, http://www.gaisler.com/notes                                                            |

| [SPWCUC]            | High Accuracy Time Synchronization over SpaceWire Networks, SPWCUC-REP-0003, Version 1.1, September 2012                                          |

| [SPWD]              | SpaceWire-D - Deterministic Control and Data Delivery over Space-<br>Wire Networks, Draft B, April 2010, ESA Contract Number 220774-<br>07-NL/LvH |

| [SPWID]             | Space engineering: SpaceWire Protocol Identification, ECSS-E-ST-50-51C, 5 February 2010                                                           |

| [SPWINT]            | Yuriy Sheynin, Distributed Interrupts in SpaceWire Interconnections,<br>International SpaceWire Conference, Nara, November 2008 (out-<br>dated)   |

| [SPWPNP]            | Space Engineering: SpaceWire Plug-and-Play protocol, ECSS-E-ST-50-54C, Draft, March 2013                                                          |

| [V8E]               | SPARC-V8 Supplement, SPARC-V8 Embedded (V8E) Architecture Specification, SPARC-V8E, Version 1.0, SPARC International Inc.                         |

| [SPWTDP]            | Spreadsheet to configure the GRSPWTDP timer, Issue 1,                                                                                             |

|                     | https://gaisler.com/doc/spwtdp/grspwtdp_settings_issue1.ods                                                                                       |

| [GRLIB-TN-<br>0021] | Level-2 Cache Issues H1 2023, GRLIB-TN-0021, http://www.gais-<br>ler.com/notes                                                                    |

## 1.8 Document revision history

Change record information is provided in table 1.

| Version | Date          | Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.0     | July 2018     | Clear 1.x revision history.<br>Add statement in section 1.1 that silicon revision 0 users should refer to version 1.x of the DS.<br>Remove silicon revision 0 specifics from sections 2.3, 2.4, 3.1, 5.9.2, 6.2.16, 6.10.8, 9.4.12, 9.4.13, 10.6.1, 10.6.2, 13.5.3, 15.6.1, 15.6.3, 21.2.10, 21.3, 22.3.10, 27.2.4, 27.3, 28.3, 29, 31.3.3, 31.3.9, 31.3.11, 31.3.12, 31.4, 39.3, 40.4, 41, 42, and 43.<br>Updated package drawings in section 40.4. In section 40.4.2 (CLGA) A, D1 and E1 have new values and F, E2 and e have limits defined. In section 40.4.3 (CCGA) A, A3, b, D1 and E1 have new values and D2, E2 and e have now limits defined.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.1     | February 2019 | Update pull-down column and clarify reserved pins in section 40.3.<br>Corrected reset value of IO port (GRGPIO) interrupt map registers in section 22.3.8<br>Add references to GRGPIO interrupt map and flag registers in section 22.2.<br>Corrected typo on AMBA port status register offset in table 154.<br>Document codec version field for MIL-STD-1553B controller in table 309.<br>Corrected description of bit 5 in AHB watchpoint control register, table 520.<br>Add note about wrapping register memory maps to section 2.3.<br>Clarify AHB status register ME behaviour in section 27.2.<br>Clarify CCGA column type in section 42.<br>Add information to footnote in section 39.2<br>Clarify that PLL ground is internally connected to GND in section 39.4<br>Correct wrong unit used in LVDS leakage value and adjust values to align with test program<br>in section 39.4.3. Also add additional heading rows to clarify division between conditions<br>and characteristics in section<br>Add more details on test methods for AC parameters, and reword first sentence in section<br>39.5.1.<br>Reword footnote on PCI compliance in section 39.5.2 and 39.5.12.<br>Maximum PLL lock time increased in section 39.5.3.<br>Update AC timings for slow interfaces (based on static timing analysis) in sections 39.5.7,<br>39.5.8, 39.5.14, 39.5.16, 39.5.17, 39.5.18 and 39.5.19.<br>Temporarily remove AC timing values under review and replace with an asterisk, to be filled<br>in with new values in next revision, in sections 39.5.5, 39.5.8. 39.5.10 and 39.5.12. |

| 2.2     | March 2019    | Document the combination of half -duplex and gigabit mode as unsupported for the Ethernet controller in sections 14.1 and 14.8<br>Update AC specifications in sections 39.5.5, 39.5.8. 39.5.10 and 39.5.12.<br>Clarify leakage specification not applicable to pins with pull-down in section 39.3<br>Update DC characteristics in section 39.3<br>Add symbol names for leakage parameters in section 39.4.3<br>Updated AC parameter test conditions in section 39.5.1<br>Renamed section 39.2 to remove the word recommended. Remove typical hysteresis value,<br>add hysteresis value for LVDS inputs, and use µA instead of uA as unit in section 39.3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.3     | May 2019      | Clarified memory scrubber threshold enable behavior in sections 11.3.3 and 11.3.9.<br>Clarified obsolete ordering codes in section 42.<br>Correct typos and make spelling consistent in sections 3.1, 6.5, 13.2.18, 13.4.8, 31.3.9,<br>34.2.1. Formatting fixes in 31.4, 39.5.3, 39.5.6<br>Remove detailed descriptions of L2C register fields that must be set to 1, in section 9.4.12<br>Clarify memory scrubber coherency note to only apply to initialization in section 11.1<br>Clarify multiple register sets in section 27.1 and add table to describe multiple error behavior<br>for the AHB status register in section 27.2.4.<br>Added legend to clarify colour coding of pins in section 40.2<br>Add minimum column and add ESD rating to absolute maximum ratings table in section<br>39.1. Add footnotes and update LVDS common mode range in operating conditions table.in<br>section 39.2. Updated input capacitance and clarified footnote 4 only applies to maximum<br>leakage value in section 39.3. Add LVDS output threshold to section 39.5.1<br>Clarify event descriptions related to Spacewire in sections 5.9.3, 22.3.11 and 31.3.10.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Version | Date           | Note                                                                                                                                                           |

|---------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.4     | September 2020 | Clarified in section 6.9.5 that instruction cache needs to be disabled for instruction cache diagnostic accesses.                                              |

|         |                | Correct FT diagnostic data register in section 10.6.6 to have rw instead of r attribute.                                                                       |

|         |                | Add section 43.2.5 to highlight that behaviour of stores to ASI 0x1C (MMU/cache bypass)                                                                        |

|         |                | may be different in GR740 compared to more recent LEON4 implementations.<br>Clarify that "gated off" means "disabled in the clock gating unit" in section 4.9. |

|         |                | Add -LG625 models for GR740-MS(E)V/Q, -DD and -DC in section 42.                                                                                               |

|         |                | LEON4 Statistics Unit time stamp register is always zero, add section 43.2.6 update sections                                                                   |

|         |                | 5.9.2 and 26.                                                                                                                                                  |

|         |                | Change section 23.2.2 to reflect that UART RTSN is always generated regardless of if flow                                                                      |

|         |                | control is enabled.                                                                                                                                            |

|         |                | Clarify in section 19.4 that the external PROM address bus range available in 8-bit mode is                                                                    |

|         |                | 27:0 and 27:1 for 16-bit                                                                                                                                       |

|         |                | Added missing note 3 and updated parameter, in table 558.                                                                                                      |

|         |                | Updated note 1, parameter and symbol in table 560.                                                                                                             |

|         |                | Added note to timing parameters in table 567.                                                                                                                  |

|         |                | Added note to timing parameters in table 569.                                                                                                                  |

|         |                | Changed minimum and maximum timing values in table 572.                                                                                                        |

|         |                | Updated note 3 in table 577.                                                                                                                                   |

|         |                | Updated note 3 in table 576.                                                                                                                                   |

|         |                | Replaced table 559 with supply currents and current levels.                                                                                                    |

|         |                | Section 39.2 is updated with ground connection requirement.                                                                                                    |

|         |                | Table 556 AMR minimum values of LVCMOS and LVDS is populated. New notes added.                                                                                 |

|         |                | Updated note 3 and added note 4 in table 557. Updated Maximum value of LVDS input dif-                                                                         |

|         |                | ferential in table 557.                                                                                                                                        |

|         |                | Updated minimum I/O level of LVCMOS in table 560. New entry added for LVDS differen-<br>tial input level in table 560.                                         |

|         |                | Updated storage temperature range and fixed missing positive sign in table 584.                                                                                |

|         |                | Added information about new simulation for LGA package in table 585.                                                                                           |

|         |                | Added new note 2 in table 572.                                                                                                                                 |

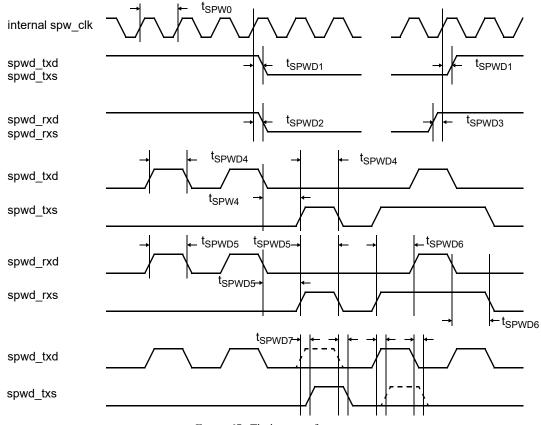

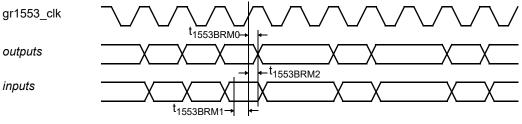

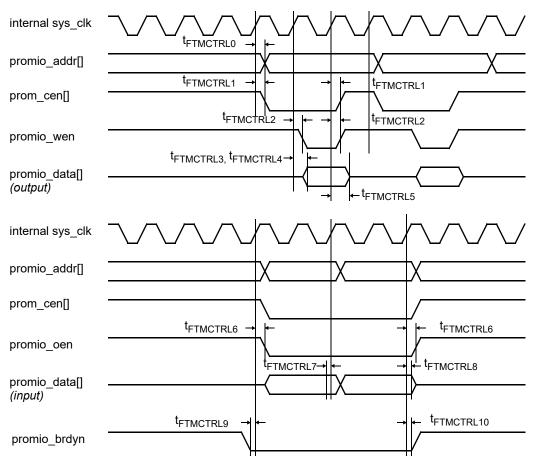

|         |                | Added notes to tSPWD4, tSPWD5 and tSPWD7 in table 571.                                                                                                         |

|         |                | Added notes to GMII clocks in table 568. Removed italics formatting of notes in table 568.                                                                     |

|         |                | Changed DLL to PLL in table 580.                                                                                                                               |

|         |                | Updated table 586 with GR740-MP-LG625 and fixed typo.                                                                                                          |

|         |                | Updated data sheet status in section 1.1 and 1.2.                                                                                                              |

|         |                | Added new note, missing symbols, updates symbols and fixed typo in table 562.                                                                                  |

|         |                | Removed signal TESTEN signal from table 28 as this is not a user pin.                                                                                          |

|         |                | Supply name updated in section 39.4.1.                                                                                                                         |

|         |                | Updated description in section 39.4.                                                                                                                           |

| 1       |                | Fixed wrong cross reference in section 39.5.11                                                                                                                 |

| Version | Date          | Note                                                                                                                                                                                                                     |

|---------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.5     | November 2021 | Added PBGA625 package type to front sheet                                                                                                                                                                                |

|         |               | Updated links in sections 1.5 and 1.6                                                                                                                                                                                    |

|         |               | Corrected incorrect number of masters in Table 138                                                                                                                                                                       |

|         |               | Updated temperature sensor enable sequence in section 29                                                                                                                                                                 |

|         |               | Corrected text regarding GPIO 11 in section 4.9                                                                                                                                                                          |

|         |               | Clarified the value of the bootstrap signal GPIO 11 Table 23                                                                                                                                                             |

|         |               | Corrected check bit width numbering in Table 89 and Table 90                                                                                                                                                             |

|         |               | Updates section 17.2                                                                                                                                                                                                     |

|         |               | Updated Table 452                                                                                                                                                                                                        |

|         |               | Added reference to SPWTDP configuration spreadsheet in section 31.3.3, Table 468 and Table 469                                                                                                                           |

|         |               | Removed information regarding external UART clock from section 23.3 and Table 23.7.3                                                                                                                                     |

|         |               | Clarified the SpaceWire interfaces that uses the Internal SpaceWire clock in Table 29                                                                                                                                    |

|         |               | VSSPLLD changed to GND in Table 556 and text about VSSPLLD and GND removed in section 39.2                                                                                                                               |

|         |               | Maximum ratings for LVCMOS and LVDS updated in Table 556 and note 1, 3 and 4                                                                                                                                             |

|         |               | Maximum Junction Temperature added to Table 556                                                                                                                                                                          |

|         |               | Editorial updates in Table 556                                                                                                                                                                                           |

|         |               | Recommended operating temperature specified per package type in Table 557 with new notes 6 and 7                                                                                                                         |

|         |               | Updated recommended operation conditions for LVCMOS in Table 557 with note 5                                                                                                                                             |

|         |               | LVDS differential parameter clarified to be absolute values in Table 557                                                                                                                                                 |

|         |               | Editorial updates in Table 559 and section 39.4.1                                                                                                                                                                        |

|         |               | Note 2 new in Table 560                                                                                                                                                                                                  |

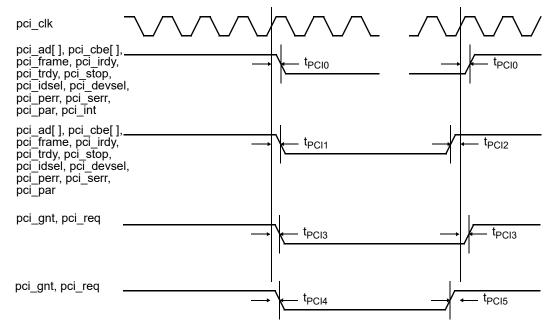

|         |               | Updated maximum PCI clock period in Table 572                                                                                                                                                                            |

|         |               | Added PBGA625 package type to section 40.1                                                                                                                                                                               |

|         |               | Added comment about placement diagram and pin assignment to section 40.1                                                                                                                                                 |

|         |               | Added that lid is connected to GND in package in section 40.4.2 and 40.4.3 and updated section headings. Added table and figure captions in these sections with editorial and format updates of Table 581 and Table 582. |

|         |               | Updated note 1 in Table 581                                                                                                                                                                                              |

|         |               | Added PBGA625 package dimensions and drawing in new section 40.4.4                                                                                                                                                       |

|         |               | Temperature limits specified per package type in Table 584 and added maximum rating.                                                                                                                                     |

|         |               | Added the thermal resistance, junction to bottom of balls in Table 585                                                                                                                                                   |

|         |               | Editorial updates in Table 584 and Table 585                                                                                                                                                                             |

|         |               | Added GR740-CP-PBGA625 and GR740-AS-PBGA625 to Table 586                                                                                                                                                                 |

|         |               | Added DC, DD and AS designator and PBGA package type to Table 587                                                                                                                                                        |

|         |               | Changed company name in several sections.                                                                                                                                                                                |

| Version | Date      | Note                                                                                            |

|---------|-----------|-------------------------------------------------------------------------------------------------|

| 2.6     | June 2023 | Fixed typo in Table 23                                                                          |

|         |           | Removed text from section 13.2.9                                                                |

|         |           | Fixed the SDRAM refresh rate calculation formula in sections 10.4.5 and 10.6.1                  |

|         |           | Removed MSEV and MSEQ products from Table 586 and Table 587                                     |

|         |           | Removed references to MSEV and MSEQ products from titles in section 40.4.2 and 40.4.3           |

|         |           | Fixed typo related to RTR.PSTSCFG register in Table 172, Table 173 and Table 179                |

|         |           | Updates related to processor's reset start address in sections 6.2.18, 6.2.19 and Table 48      |

|         |           | Corrected error detection order id in sections 13.4.6.2 and 35.7.2                              |

|         |           | Removed incomplete sentence in the footnote of Table 154                                        |

|         |           | Corrected typo in Table 174                                                                     |

|         |           | Fixed controller setting bit value in Table 86                                                  |

|         |           | Clarified count block size in section 11.2.4                                                    |

|         |           | Clarified the error count threshold behavior in sections 11.2.1, 11.2.4, 11.3.3 and 11.3.9      |

|         |           | Clarification about first setting SDCFG1.RF field in section 10.4.8                             |

|         |           | Clarification about updating the SDCFG2.EN2T field in section 10.6.2                            |

|         |           | Clarification to SDRAM initialization in section 10.4.2                                         |

|         |           | Mention about JTAG boundary scan in section 34.1                                                |

|         |           | Fixed incorrect LVCMOS IO level, recommended minimum value in Table 560                         |

|         |           | Temperature sensor measurement unit clarification in section 29.1 and Table 447                 |

|         |           | Default drive strength value updated in section 30.3.7                                          |

|         |           | Removed irrelevant condition in 23.7.3                                                          |

|         |           | Fixed incorrect FIFO capacity in section 13.3                                                   |

|         |           | Clarification to the FIFOs in Figure 13 and Figure 14                                           |

|         |           | Clarification about drive strength in section 30.2.3 and 30.3.7                                 |

|         |           | Updated input filtering scheme description under 23.2.2                                         |

|         |           | FIFO size clarification under section 23.1 and Figure 40                                        |

|         |           | Clarified the SpW Router role in tx/rx of time codes and RMAP packets in 31.3,31.3.4 and 31.3.5 |

|         |           | CUC example preamble field reflects the coarse and fine time implemented in GR740 in            |

|         |           | Table 461                                                                                       |

|         |           | Clarification about unimplemented jitter and drift mitigation unit in section 31.3.8            |

|         |           | Removed unimplemented registers in section 31.4                                                 |

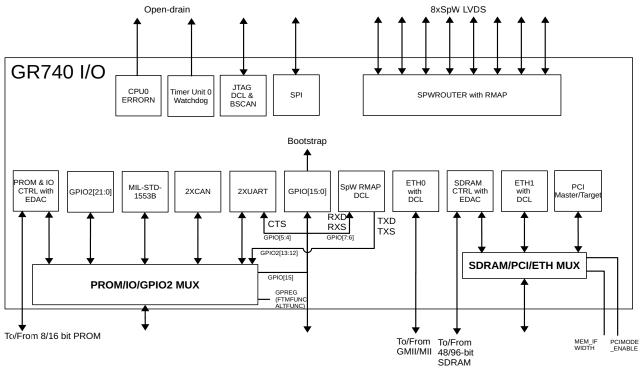

|         |           | Added GR740 I/O structure and pin multiplexing diagram under section 3.3                        |

|         |           | Fixed incorrect start address for APBBRIDGE, marked unused memory range in Table 8              |

|         |           | Added PROC ERRORN errata in section 43.2.7                                                      |

|         |           | Added clarification notes in Table 556 and Table 557                                            |

|         |           | Added reference to actual LVDS electrical characteristics in section 13                         |

|         |           | Additional information related to the COMMAND field in section 10.4.8                           |

|         |           | New errata related to SDRAM COMMAND field documentation in section 43.2.8                       |

|         |           | Seven items added under L2C issues H1 2023errata in section 43.2.9                              |

|         |           | New reference document GRLIB-TN-0021 added to section 1.7                                       |

|         |           | Added new errata titles to Table 588                                                            |

|         |           | Fixed description related to external clock enable in Table 372                                 |

|         |           | Corrected incorrect heading in section 9.2                                                      |

|         |           | Removed mention about unavailable signal in Table 155                                           |

|         |           | Added clarification about the GPTIMER0 tick signals in section 22.2                             |

|         |           | Changed text 'GPTIMER 0' to GPTIMER0 in whole document.                                         |

Table 1. Change record

| Version | Date       | Note                                                                                       |

|---------|------------|--------------------------------------------------------------------------------------------|

| 2.7     | March 2024 | Added GRETH Gbit incorrect packet detection errata in section 43.2.10                      |

|         |            | Added SDRAM refresh rate calculation formula documentation error errata in section 43.2.11 |

|         |            | Added MEM_CLK_IN to Table 29                                                               |

|         |            | Updated footnote 8 in Table 557                                                            |

|         |            | Fixed typo in Table 350                                                                    |

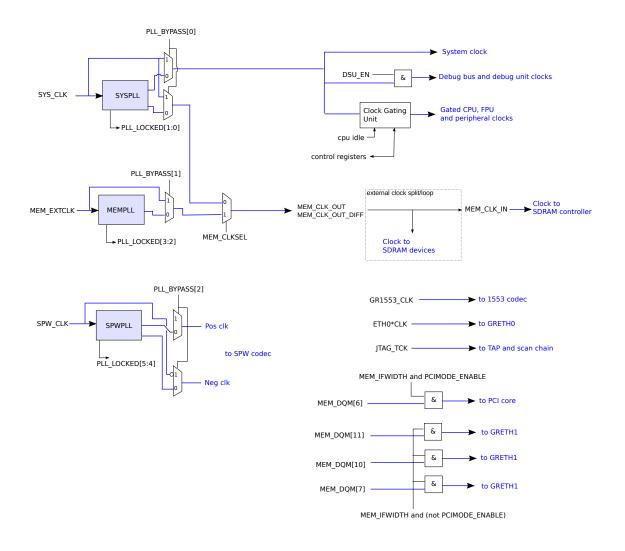

|         |            | Updated Figure 1 indicating pin sharing between GPIO2 and SPW TX                           |

|         |            | Updated architecture detailed block diagram on front page and under section 2.1            |

|         |            | Clarified CAN channel disabling behavior in section 17.5.7                                 |

|         |            | Updated access field values in Table 82                                                    |

|         |            | Clarified the GPIO lines that can generate interrupt in GRGPIO1 in section 22.1            |

|         |            | Fixed incorrect access permission detail in Table 279 and Table 278                        |

|         |            | Fixed reset value of ENDIAN in Table 260                                                   |

|         |            | Clarified that autoscrub is enabled in SpaceWire router in section 13.2.22 and 13.2.22.1   |

|         |            | Updated register bit descriptions in Table 160                                             |

|         |            | Fixed swapped register field descriptions in Table 323                                     |

|         |            | Rephrased SW-node to SpaceWire controller in Table 160 and SPW2.DMACTRLin Table 535        |

|         |            | Fixed incorrect register offset in Table 81                                                |

|         |            | Fixed incorrect register field bit numbering in Table 77                                   |

|         |            | Added initial signal state on system power up under section 3.6                            |

|         |            | Added SPWROUTER false positive memory error erratum in section 43.2.12                     |

|         |            | Clarified MCFG5.IOHWS and MCFG5.ROMHWS field descriptions in section 19.9.3                |

|         |            | Clarified clear-on-write behavior for register bit 19 and 20 in Table 273                  |

|         |            | Fixed incorrect hypertext in Table 7                                                       |

|         |            | Company name changed to Frontgrade Gaisler in sections 1.4, 6.2.3 and Table 210            |

| Version | Date          | Note                                                                                                                    |

|---------|---------------|-------------------------------------------------------------------------------------------------------------------------|

| 2.8     | December 2024 | Version update.                                                                                                         |

|         |               | Corrected psr.pil field value as NR in Table 46                                                                         |

|         |               | Corrected asr16.fpce and asr16.iuce field values as NR in Table 49                                                      |

|         |               | Corrected ASI 0x2 df and if field values as NR in Table 55                                                              |

|         |               | Corrected ASI 0x19, offset 0x300 - FSR - MMU Fault Status Register in Table 60                                          |

|         |               | Fixed typo and added reset value for ASI 0x2, 0x08 and 0x0C repl field in Table 56                                      |

|         |               | Fixed typo in Table 58                                                                                                  |

|         |               | Clarified the memscrub error counter increment in 11.2.4                                                                |

|         |               | Added details of new quality level available for GR740 in Table 586, Table 587, Table 557, Table 584 and section 40.4.4 |

|         |               | Fixed reset value of TH bit field in 23.7.2                                                                             |

|         |               | Clarified JTAG_TRST signal value during power up sequence in section 39.4.1                                             |

|         |               | Corrected the register bit name in 16.4.2                                                                               |

|         |               | Error response propagation clarified in 19.8                                                                            |

|         |               | PLL_LOCKED signal bit description added in section 4.5                                                                  |

|         |               | Bootstrap register width corrected in section 28.2                                                                      |

|         |               | L2cache hit event count in l4stat is clarified in Table 433                                                             |

|         |               | Clarified state of the CPU after placing it in error mode in section 21.2.10                                            |

|         |               | Added a summary about timer tick out signal mapping in GR740 in section 20.2                                            |

|         |               | Scrubber initialization data register clarified in sections 11.2.7 and 11.3.10                                          |

|         |               | Errata placeholder added in section 43.2.13                                                                             |

|         |               | Fixed the missing LE bit in section 13.4.5.4                                                                            |

## 1.9 Acronyms

Table 2. Acronyms

| Acronym     | Comment                                                                                                                   |

|-------------|---------------------------------------------------------------------------------------------------------------------------|

| AHB         | Advanced High-performance bus, part of [AMBA]                                                                             |

| AMBA        | Advanced Microcontroller Bus Architecture                                                                                 |

| AMP         | See ASMP                                                                                                                  |

| APB         | Advanced Peripheral Bus, part of [AMBA]                                                                                   |

| ASMP        | Asymmetric Multi-Processing (in the context of this document: different OS instances run-<br>ning on own processor cores) |

| BCH         | Bose-Hocquenghem-Chaudhuri, class of error-correcting codes                                                               |

| CAN         | Controller Area Network, bus standard                                                                                     |

| CPU         | Central Processing Unit, used to refer to one LEON4 processor core.                                                       |

| DCL         | Debug Communication Link. Provides a bridge between an external interface and on-chip AHB bus.                            |

| DDR         | Double Data Rate                                                                                                          |

| DMA         | Direct Memory Access                                                                                                      |

| DSU         | Debug Support Unit                                                                                                        |

| EDAC        | Error Detection and Correction                                                                                            |

| EDCL        | Ethernet Debug Communication Link                                                                                         |

| FIFO        | First-In-First-Out, refers to buffer type                                                                                 |

| FPU         | Floating Point Unit                                                                                                       |

| Gb          | Gigabit, 10 <sup>9</sup> bits                                                                                             |

| GB          | Gigabyte, 10 <sup>9</sup> bytes                                                                                           |

| GiB         | Gibibyte, gigabinary byte, 2 <sup>30</sup> bytes, unit defined in IEEE 1541-200                                           |

| I/O         | Input/Output                                                                                                              |

| IP, IPv4    | Internet Protocol (version 4)                                                                                             |

| ISR         | Interrupt Service Routine                                                                                                 |

| JTAG        | Joint Test Action Group (developer of IEEE Standard 1149.1-1990)                                                          |

| kB          | Kilobyte, 10 <sup>3</sup> bytes                                                                                           |

| KiB         | Kibibyte, 2 <sup>10</sup> bytes, unit defined in IEEE 1541-2002                                                           |

| L2          | Level-2, used in L2 cache abbreviation                                                                                    |

| MAC         | Media Access Controller                                                                                                   |

| Mb, Mbit    | Megabit, 10 <sup>6</sup> bits                                                                                             |

| MB, Mbyte   | Megabyte, 10 <sup>6</sup> bytes                                                                                           |

| MiB         | Mebibyte, 2 <sup>20</sup> bytes, unit defined in IEEE 1541-2002                                                           |

| OS          | Operating System                                                                                                          |

| PCI         | Peripheral Component Interconnect                                                                                         |

| PROM        | Programmable Read Only Memory. In this document used to signify boot-PROM.                                                |

| RAM         | Random Access Memory                                                                                                      |

| RMAP        | Remote Memory Access Protocol                                                                                             |

| SEE         | Single Event Effects                                                                                                      |

| SEL/SEU/SET | Single Event Latchup/Upset/Transient                                                                                      |

#### Table 2. Acronyms

| Acronym | Comment                                     |

|---------|---------------------------------------------|

| SMP     | Symmetric Multi-Processing                  |

| SPARC   | Scalable Processor ARChitecture             |

| ТСР     | Transmission Control Protocol               |

| UART    | Universal Asynchronous Receiver/Transmitter |

| UDP     | User Datagram Protocol                      |

### 1.10 Definitions

This section and the following subsections define the typographic and naming conventions used throughout this document.

#### 1.10.1 Bit numbering

The following conventions are used for bit numbering:

- The most significant bit (MSb) of a data type has the leftmost position

- The least significant bit of a data type has the rightmost position

- Unless otherwise indicated, the MSb of a data type has the highest bit number and the LSb the lowest bit number

#### 1.10.2 Radix

The following conventions is used for writing numbers:

- Binary numbers are indicated by the prefix "0b", e.g. 0b1010.

- Hexadecimal numbers are indicated by the prefix "0x", e.g. 0xF00F

- Unless a radix is explicitly declared, the number should be considered a decimal.

#### 1.10.3 Data types

| Byte (BYTE)         | 8 bits of data   |

|---------------------|------------------|

| Halfword (HWORD)    | 16 bits of data  |

| Word (WORD)         | 32 bits of data  |

| Double word (DWORD) | 64 bits of data  |

| Quad word (4WORD)   | 128-bits of data |

## 1.11 Register descriptions

An example register, showing the register layout used throughout this document, can be seen in table 3. The values used for the reset value fields are described in table 4, and the values used for the field type fields are described in table 5. Fields that are named RESERVED, RES, or R are read-only fields. These fields can be written with zero or with the value read from the same register field.

Table 3. <Address> - <Register acronym> - <Register name>

| 31 | 24                                     | 23 16                                  | 15 8                                   | 7 0                                    |

|----|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|

|    | EF3                                    | EF2                                    | EF1                                    | EF0                                    |

|    | <reset ef3="" for="" value=""></reset> | <reset ef2="" for="" value=""></reset> | <reset ef1="" for="" value=""></reset> | <reset ef0="" for="" value=""></reset> |

|    | <field ef3="" for="" type=""></field>  | <field ef2="" for="" type=""></field>  | <field ef1="" for="" type=""></field>  | <field ef0="" for="" type=""></field>  |

| 31: 24 | Example field 3 (EF3) - <field description=""></field> |

|--------|--------------------------------------------------------|

| 23: 16 | Example field 2 (EF2) - <field description=""></field> |

| 15:8   | Example field 1 (EF1) - <field description=""></field> |

| 7: 0   | Example field 0 (EF0) - <field description=""></field> |

Table 4. Reset value definitions

| Value | Description                                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------|

| 0     | Reset value 0.                                                                                                                 |

| 1     | Reset value 1. Used for single-bit fields.                                                                                     |

| 0xNN  | Hexadecimal representation of reset value. Used for multi-bit fields.                                                          |

| 0bNN  | Binary representation of reset value. Used for multi-bit fields.                                                               |

| NR    | Field not reset                                                                                                                |

| *     | Special reset condition, described in textual description of the field. Used for example when reset value is taken from a pin. |

| -     | Don't care / Not applicable                                                                                                    |

#### Table 5. Field type definitions

| Value | Description                                                                                         |

|-------|-----------------------------------------------------------------------------------------------------|

| r     | Read-only. Writes have no effect.                                                                   |

| w     | Write-only. Used for a writable field in a register where the field's read-value has no meaning.    |

| rw    | Readable and writable.                                                                              |

| rw*   | Readable and writable. Special condition for write, described in textual description of field.      |

| wc    | Write-clear. Readable, and cleared when written with a 1                                            |

| cas   | Readable, and writable through compare-and-swap. Only applies to SpaceWire Plug-and-Play registers. |

## 2 Architecture

## 2.1 Overview

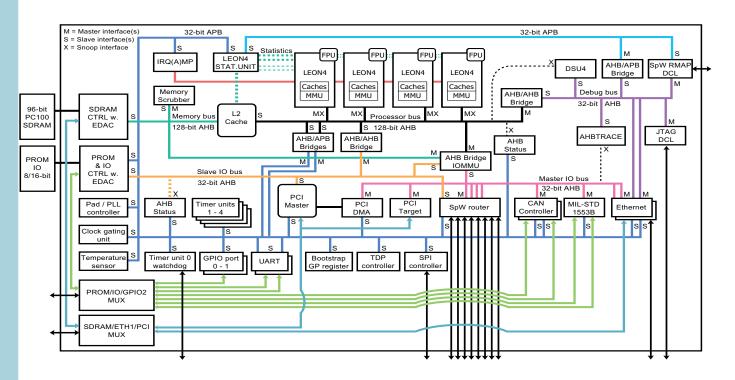

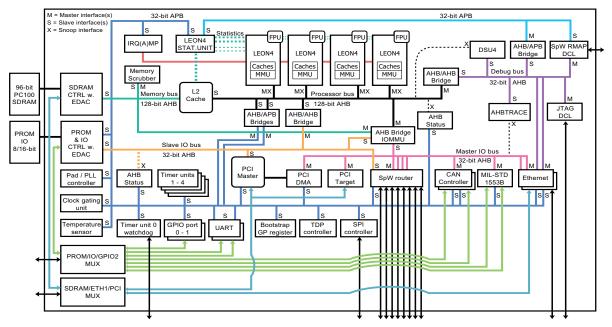

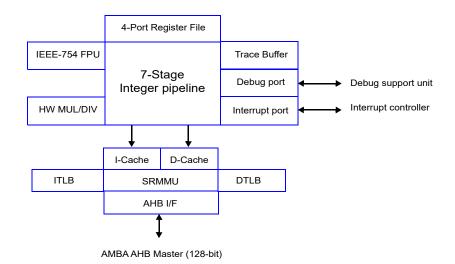

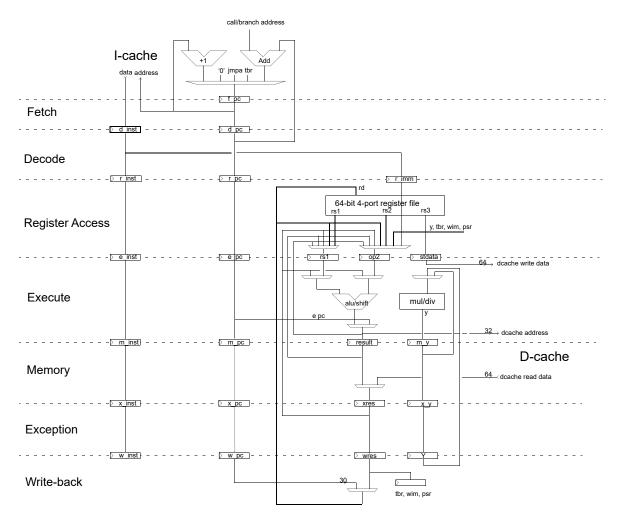

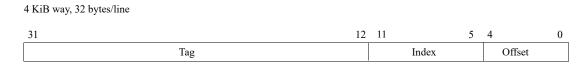

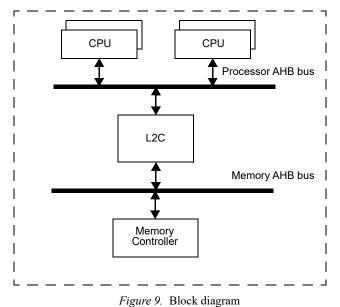

The system is built around five AMBA AHB buses; one 128-bit Processor AHB bus, one 128-bit Memory AHB bus, two 32-bit I/O AHB buses and one 32-bit Debug AHB bus. The Processor AHB bus houses four LEON4FT processor cores connected to a shared L2 cache. The Memory AHB bus is located between the L2 cache and the main external memory interface (SDRAM) and attaches a memory scrubber.